目錄表

MCRTsim v2.8

A simulation framework for DVFS-capable Multi-core Real-Time Systems.

Introduction

MCRTsim is an open source task scheduling simulator, or real-time systems with uniprocessors, multiprocessors, and multi-core processors. It contains a task set generator, a set of real-time schedulers and synchronization protocols, and a comprehensive set of tools including visualized execution tracer, schedulability analyzer, and measurement and statistic modules. Therefore, we can easy to evaluate the performance of existing scheduling algorithms as well as synchronization protocols by using MCRTsim. Furthermore, MCRTsim also contains a Java class library for supporting the design of new scheduling and synchronization protocols with minimum efforts. Another key feature of MCRTsim is the supporting of DVFS-capable processors so that the capabilities of energy-aware scheduling algorithms and synchronization protocols can be better understand.

People

Project Leader:Dr. Jun Wu.

Project Members:Shiu-Jia Hong, Yu-Cheng Huang and Hsin-Hsien Yu

Development Tools

- NetBeans 8.0.2

- JAVA language

- JDK 8

Algorithms

- Partition Algorithm:FF, FFD, BF, BFD, WF, WFD, SBP

- DVFS energy-efficient algorithms:BS, BTS, BATS, CSMS, DUAL, MS

- Scheduling Algorithm:RMS, DMS, EDF, FCFS, LST, PRMS, PDMS, PEDF, PFCFS, PLST, GRMS, GDMS, GEDF

- Synchronization Protocol:NPCS, PIP, PCP, DPCP, SRP, MSRP, MrsP, G_FMLP, P_FMLP

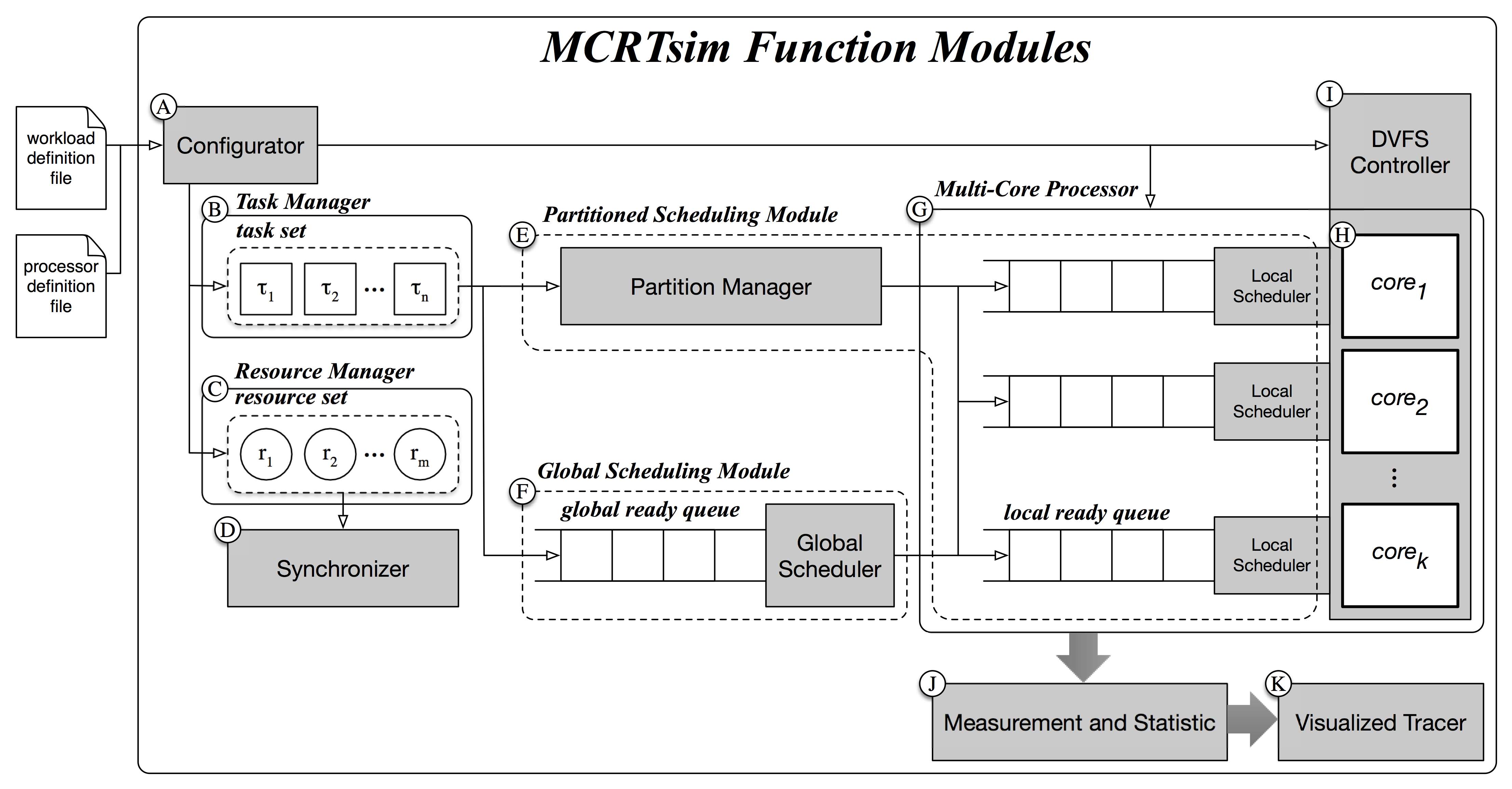

MCRTsim Function Modules

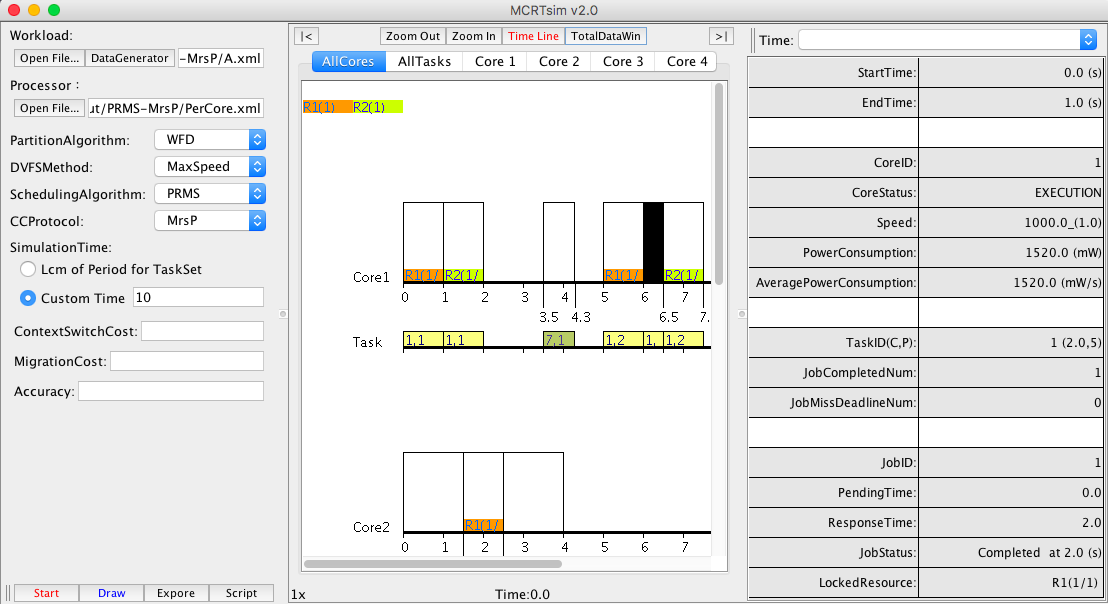

User Interface

Download

Example Experimental Settings (from a paper submitted to RACS 2018)

Last Updated

— 2018/06/30 18:32 : 發佈MCRTsim v2.8

— 2017/11/01 11:55 : 發佈MCRTsim v2.0

— 2017/05/08 19:48 : 發佈MCRTsim v1.0

— 2016/06/01 13:50 : 發佈MCRTsim v0.1

Publications about MCRTsim

- Jun Wu and Yu-Cheng Huang, MCRTSim: A Simulation Tool for Multi-core Real-Time Systems, IEEE International Conference on Applied System Innovation (ICASI 2017), Sapporo, Japan, May 13-17, 2017.

Publications using MCRTsim

- Manal A. El Sayed,El Sayed M. Saad, Rasha F. Aly, and Shahira M. Habashy, Energy-Efficient Task Partitioning for Real-Time Scheduling on Multi-Core Platforms, Computers 2021, 10(1), 10(https://doi.org/10.3390/computers10010010).

- M. A. El Sayed, M. S. El Sayed, S. M. Habashy and R. F. Aly, “Online DVFS Scheduling Algorithm for Sporadic Tasks with Energy-Conscious in Hard Real-Time Systems,” 2021 16th International Conference on Computer Engineering and Systems (ICCES), Cairo, Egypt, Egypt, 2021, pp. 1-7.

- S. Palamut, T. Gönültaş, A. Elewi and E. Avaroğlu, “Task Scheduling Algorithms and Resource Access Protocols in Real Time Systems,” 2019 International Artificial Intelligence and Data Processing Symposium (IDAP), Malatya, Turkey, 2019, pp. 1-6.

- Jun Wu and Hsin-Hsien Yu, A Comparison of Energy-Efficient Strategies for Real-Time Task Synchronization Protocols, ACM Research in Adaptive and Convergent Systems (RACS 2018), Honolulu, Hawaii, October 9-12, 2018.

- Jun Wu and Xu-Jia Hong, Energy-Efficient Task Scheduling and Synchronization for Multicore Real-Time Systems, 3rd IEEE International Conference on High Performance and Smart Computing (HPSC 2017), Beijing, China, May 2017